“IC封装工艺介绍”总结

“IC封装工艺介绍”总结

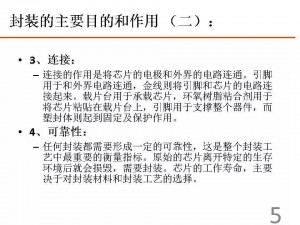

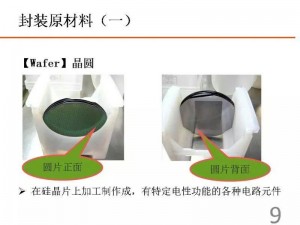

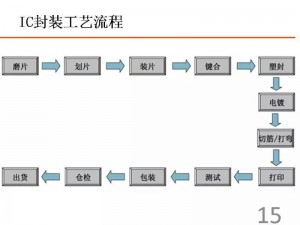

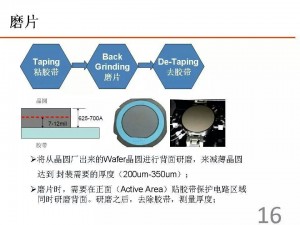

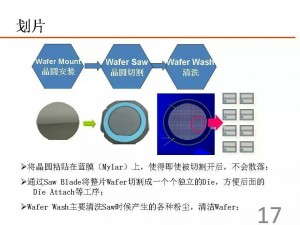

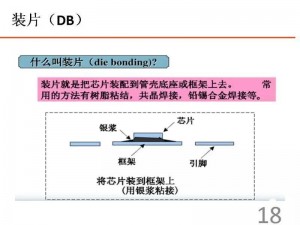

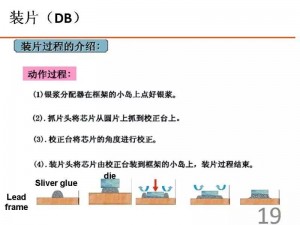

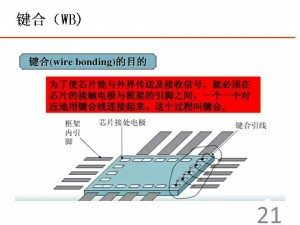

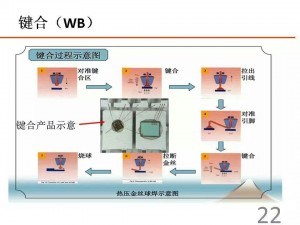

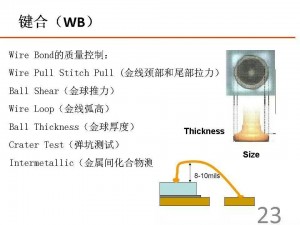

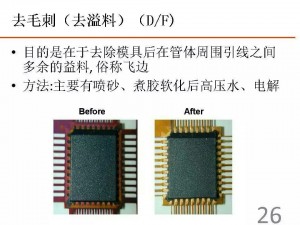

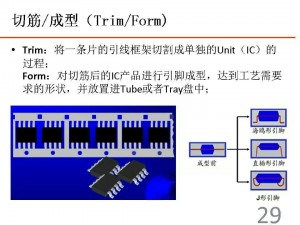

封装的工序比较复杂,大概有十几道工序,有磨片、划片……磨片就是让圆片背面减薄,适应封装需要;划片就是通过金属刀片,让晶圆能够一粒一粒地分割出来;装片就是通过导电胶,让芯片跟引线框固定起来;键合就是通过芯片的pad与框架之间实现电路导通;塑封就是把产品包装起来。里面的关键工序是“键合和塑封”,键合实现了我们的目的,塑封对键合实现品质保证和产品的可靠性。

问答讨论环节:

1.陈同学:磨片厚度和什么有关系?现在saw blade的宽度最小能到多少?

封装尺寸。咨询了下我们的划片工程师,目前我司的最小能做到60um。

2.温同学: 今天分享介绍的封装工艺中最具挑战性的是哪个步骤?

WB(Wire Bonding键合工艺)。主要是封装集成度高,线密,对塑封后冲丝,打线是否打到Pad硅层,线弧线长控制,还有就是WB拉力,推力,lMC控制。另外就是封装的分层控制,系统工程。

3.郑同学:环氧树脂可以通过印刷的方式涂吗?

应该说的是CoB封装,点黑胶固化,可能通过印刷的方式。这个具体可以让群里的中鹏塑料销售总监叶总,材料专家回答下。

4.叶同学: 固化一般多长时间? 看过某小工厂后固化就2小时,时间短有什么影响?

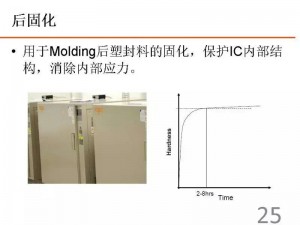

前固化一般加N2一小时,后固化传统都是6~8小时,具体参考材料TDS。后固化时间短会导致应力释放不充分,可靠性受影响。

5.叶同学: 划片蹦角成测能测出来吗?

划片有蹦角,一般没检出来的话在成测时会有漏电。划片蹦边,要看iC的功效及蹦角的具体部位及大小,一般来讲是不允许有大蹦角出现,会引起可靠性失效,成测可能会卡住也有可能会漏测,之前我们遇到过产品测试idd失效,经腐开试验确认是划片磞角引起漏电失效。

6.陈同学:这些工艺步骤中,哪些会是高温?最高温度会超过400度么?

WB因焊丝及芯片关系,铜线一般比金线略高,一般控制在180~240度主焊区,MD控制在175士5度左右,共晶控制在400度左右。

7.郑同学: 共晶指球封么?

不是,共晶是支架与圆片芯片背金形式DB结合,BGA才是指球封。

8.叶同学: 什么时候共晶和什么情况焊料? 共晶还要打线么?

共晶是支架与圆片芯片背金形式DB结合,焊料一般适用于T0大功率器件,易散热,是DB的几种实现工艺,跟芯片结构功能及实现封装形式关联。DB时,支架与圆片共晶结合。共晶是DB,WB是打线,倒装不需要打线。

9.罗同学:封测设备都能国产化了吗?有没那块还做不了的?

封测设备及材料有在实现国产化,大多数国产设备及材料都能达到行业工艺水准,基本都能实现产业化。

10.郑同学: 封装的成本高吗?比如说占ic成本的比例?

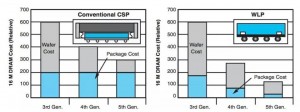

1)参考某同学从网上搜索到的DRAM CSP与WLCSP的封装成本与芯片成本的大致比例。

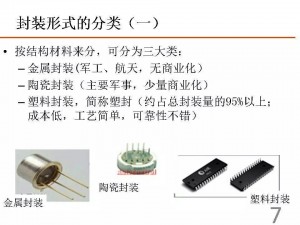

2)这个问题跟不同的产品线有关,一些consumer的产品,直接cob,省了塑封的钱,可靠性差一点。某个同学举了光电芯片的例子: 光电芯片的芯片成本1美金,封装成本可能要100美金,然后卖200美金。可能与大部分芯片的成本组成都不同。只要封装交付的,用陶瓷封装成本还可以,用golden box就最贵了,也有一些芯片是裸片交付,然后系统方把很多芯片都封装在一起,降低封装成本。

11.郑同学: 什么情况下选择划片封装?什么情况会考虑晶圆级封装?

WL-CSP与传统的封装方式不同在于,传统的晶片封装是先切割再封测,而封装后约比原晶片尺寸增加20%;而WL-CSP则是先在整片晶圆上进行封装和测试,然后才划线分割,因此,封装后的体积与IC裸芯片尺寸几乎相同,能大幅降低封装后的IC 尺寸。

—————-

分享嘉宾简介:

李二成,封装工程师,就职于深圳晶宝微。河南舞阳人,喜欢交友,学习,旅游,华南师范大学本科。

微信扫一扫

关注该公众号

………..………..….……….……………………..

半导体行业分享 | www.kanwoda.com | 微信icshare52

本文地址: http://www.kanwoda.com/blog/archives/0721192109839.html