运放测试电路自激振荡与仿真

我们知道,运放在实际应用中可能会出现自激振荡现象,基于辅助运放的测试电路也是这样。自激振荡一旦产生,轻则导致测试时间增加,严重的话,会导致测试结果不准确,产生质量隐患。

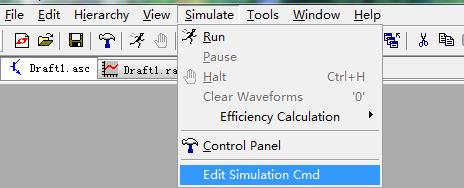

下面我们用 LTSpice IV 来仿真一下。(《测试基础篇-电容与电感对电流测试的影响》 文中有 LTSpice IV 的下载链接。)

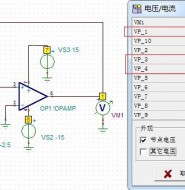

电路画好之后,可参考下面来设置,截止时间设置为10mS。

图1

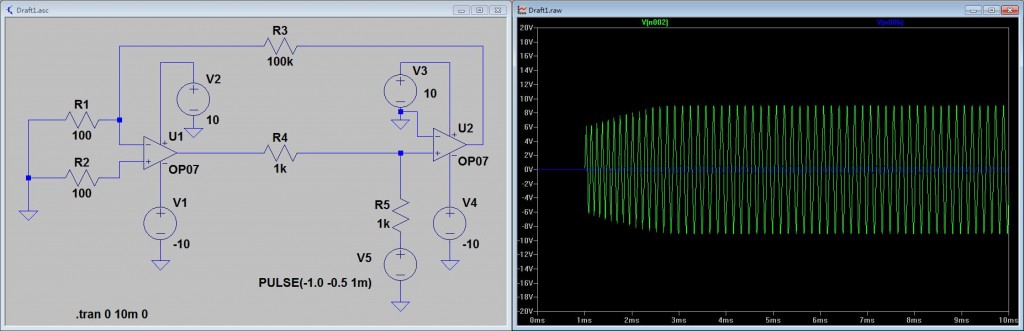

如下图2,左图是测试电路模拟,V5设置为Pulse模式。右图是U2输出端的仿真波形。我们可以清楚的看到输出在振荡。

图2

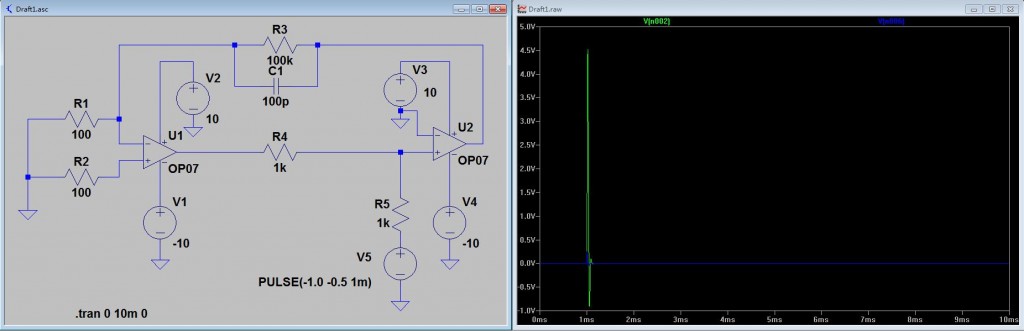

那要如何解决这个问题呢?最简单的方法,就是在反馈电阻上并联一个小电容(移相电容)来防止运放自激,一般取皮法级别,看工作的频率以及运放的型号来定。

如下图3,R3并联一个100pF的电容后,输出波形就没有产生持续的振荡了,问题解决!

图3

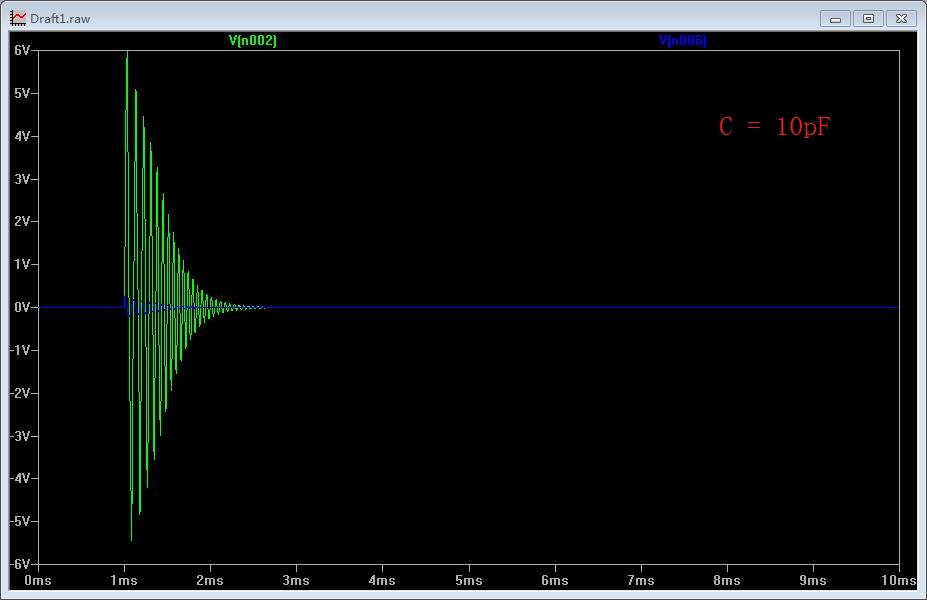

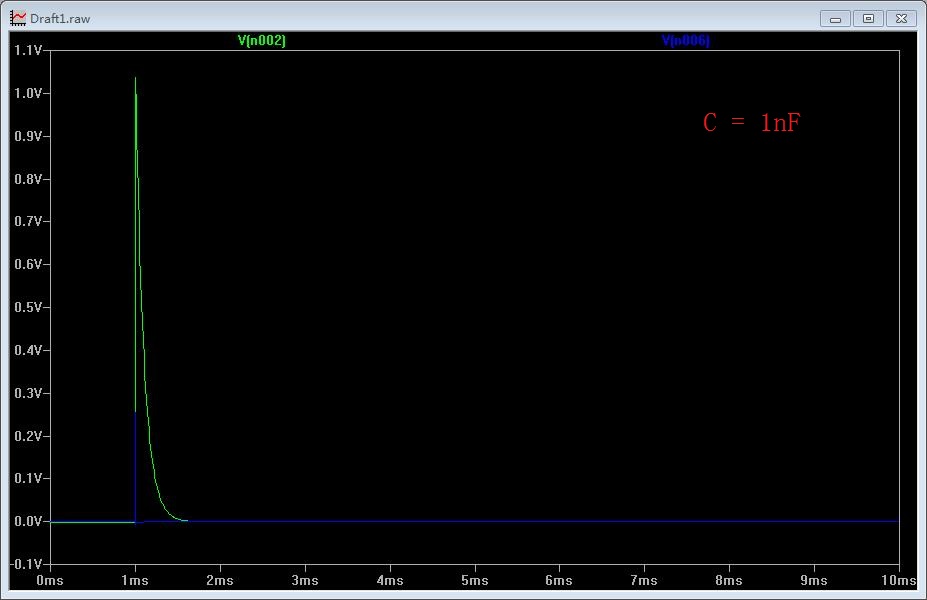

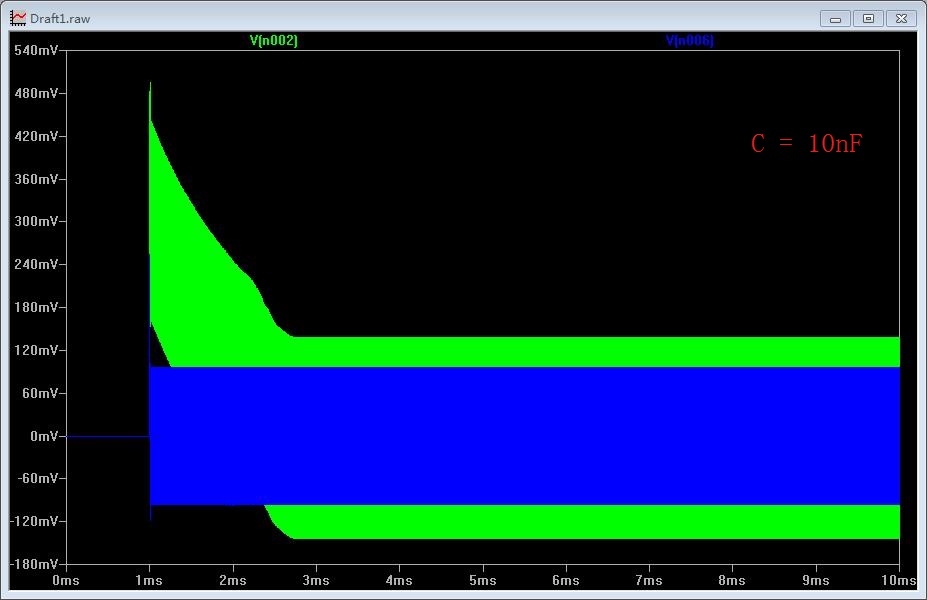

不同大小的电容对测试结果有很大影响,我们可以通过软件来仿真一下。如下图分别为C = 10pF 、 1nF、10nF时的输出波形。

图4

并不是所有的运放都会产生自激振荡,有兴趣的朋友不妨更换不同型号运放来试试看。事实上,我们在实际测试调试的过程中,也会发现,同一个测试电路并不能适用于所有的运算放大器。而这些所有的细节,都是我们工程师需要注意的。

本文地址: http://www.kanwoda.com/blog/archives/08232321301339.html